## RICE UNIVERSITY

# Lazy Release Consistency for Distributed Shared Memory

by

## Peter Keleher

A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE

## **Doctor of Philosophy**

APPROVED, THESIS COMMITTEE:

Willy Zwaenepoel, Professor, Chairman Computer Science

Alan Cox, Assistant Professor Computer Science

John Bennett, Associate Professor Electrical and Computer Engineering

Houston, Texas

January, 1995

# Lazy Release Consistency for Distributed Shared Memory

Peter Keleher

## Abstract

A software distributed shared memory (DSM) system allows shared memory parallel programs to execute on networks of workstations. This thesis presents a new class of protocols that has lower communication requirements than previous DSM protocols, and can consequently achieve higher performance. The lazy release consistent protocols achieve this reduction in communication by piggybacking consistency information on top of existing synchronization transfers. Some of the protocols also improve performance by *speculatively* moving data.

We evaluate the impact of these features by comparing the performance of a software DSM using lazy protocols with that of a DSM using previous *eager* protocols. We found that seven of our eight applications performed better on the lazy system, and four of the applications showed performance speedups of at least 18%. As part of this comparison, we show that the cost of executing the slightly more complex code of the lazy protocols is far less important than the reduction in communication requirements. We also compare the lazy performance with that of a hardware supported shared memory system that uses processors and caches similar to those of the workstations running our DSM. Our DSM system was able to approach, and in one case even surpass, the performance of the hardware system for applications with coarse-grained parallelism, but the hardware system performed significantly better for programs with fine-grained parallelism.

Overall, the results indicate that DSMs using lazy protocols have become a viable alternative for high-performance parallel processing.

## Acknowledgments

I wish to thank my committee, Willy Zwaenepoel, Alan Cox, and John Bennett, for their guidance on my thesis. Together with Sandhya Dwarkadas, they have provided me with advice, encouragement, and support throughout my graduate career. I am also indebted to them for the opportunity of working in a first-class research environment, whose excellence I am starting to appreciate only as I leave Rice.

My time at Rice was made special by many friends. Ervan, John, Nat, Mootaz, and Uli all helped make life as a graduate student a Good Thing. However, I may not have survived without Chau-Wen, who showed the way out, Reinhard, who taught that a hike in the mountains or a good bike ride cures all ills, and Jerry, who was always happy to match his frustrations against mine on the squash court.

Most of all, I would like to thank my wife, who makes everything worthwhile.

# Contents

|          | Abs                      | tract                               | ii      |  |  |  |

|----------|--------------------------|-------------------------------------|---------|--|--|--|

|          | Ack                      | nowledgments                        | <br>111 |  |  |  |

|          | List                     | of Illustrations                    | vii     |  |  |  |

|          | List                     | of Tables                           | Х       |  |  |  |

| 1        | Introduction             |                                     |         |  |  |  |

|          | 1.1                      | Programming Model                   | 2       |  |  |  |

|          | 1.2                      | Challenges                          | 3       |  |  |  |

|          | 1.3                      | Lazy Release Consistency            | 4       |  |  |  |

|          | 1.4                      | Thesis                              | 5       |  |  |  |

|          | 1.5                      | Contributions                       | 6       |  |  |  |

| <b>2</b> | Lazy Release Consistency |                                     |         |  |  |  |

|          | 2.1                      | Application Program Interface (API) | 8       |  |  |  |

|          | 2.2                      | Lazy Release Consistency            | 9       |  |  |  |

|          |                          | 2.2.1 Motivation and Background     | 9       |  |  |  |

|          |                          | 2.2.2 Release Consistency           | 11      |  |  |  |

|          |                          | 2.2.3 Lazy Release Consistency      | 13      |  |  |  |

|          |                          | 2.2.4 Happened-Before-1             | 15      |  |  |  |

|          | 2.3                      | Protocols                           | 17      |  |  |  |

|          |                          | 2.3.1 Lazy Invalidate               | 18      |  |  |  |

|          |                          | 2.3.2 Lazy Hybrid                   | 28      |  |  |  |

|          |                          | 2.3.3 Eager Invalidate              | 29      |  |  |  |

|          | 2.4                      | Correctness                         | 32      |  |  |  |

|          | 2.5                      | Summary                             | 34      |  |  |  |

| 3        | Performance 37           |                                     |         |  |  |  |

|          | 3.1                      | Experimental Environment            | 38      |  |  |  |

|          |                          | 3.1.1 Hardware Platform             | 38      |  |  |  |

|          |               | 3.1.2  | Basic Operation Costs                        |

|----------|---------------|--------|----------------------------------------------|

|          | 3.2           | Applie | ations                                       |

|          | 3.3           | Comp   | arative Evaluation                           |

|          |               | 3.3.1  | Results                                      |

|          |               | 3.3.2  | Execution Time Breakdown                     |

|          |               | 3.3.3  | Evaluation of the hybrid heuristic           |

|          | 3.4           | Perfor | mance Prediction                             |

|          |               | 3.4.1  | Simulation Methodology                       |

|          |               | 3.4.2  | Effect of Communication Software Speed       |

|          |               | 3.4.3  | Effect of Network Speed                      |

|          | 3.5           | Summ   | ary                                          |

| 4        | Sof           | tware  | e versus Hardware 76                         |

|          | 4.1           | Perfor | mance                                        |

|          |               | 4.1.1  | Experimental Platforms                       |

|          |               | 4.1.2  | Application Suite                            |

|          |               | 4.1.3  | Results                                      |

|          | 4.2           | Simul  | ation                                        |

|          |               | 4.2.1  | Simulation Models                            |

|          |               | 4.2.2  | Validation                                   |

|          |               | 4.2.3  | Results                                      |

|          |               | 4.2.4  | Reduced Software Overhead                    |

|          | 4.3           | Summ   | ary                                          |

| <b>5</b> | $\mathbf{Re}$ | lated  | Work 94                                      |

|          | 5.1           | Softwa | are-Supported Shared Memory                  |

|          | 5.2           |        | vare-Supported Shared Memory                 |

|          | 5.3           |        | ined Hardware/Software Approaches            |

| 6        | Co            | nclus  | ions and Future Work 100                     |

| U        | 6.1           | Concl  |                                              |

|          | 6.2           |        | e Work                                       |

|          |               | 6.2.1  | Integrated Parallel Programming Environments |

|          |               | 6.2.2  | Fault Tolerance   102                        |

V

Bibliography

104

# Illustrations

| 1.1  | Distributed Shared Memory                                                                           | 2  |

|------|-----------------------------------------------------------------------------------------------------|----|

| 2.1  | Simple DSM program                                                                                  | 10 |

| 2.2  | Not SC $(x, y \text{ initially zero})$                                                              | 11 |

| 2.3  | SC $(x, y \text{ initially zero})$                                                                  | 11 |

| 2.4  | Categorization of Writable Accesses                                                                 | 12 |

| 2.5  | Eager Release Consistency                                                                           | 14 |

| 2.6  | Lazy Release Consistency                                                                            | 15 |

| 2.7  | Page State Transitions                                                                              | 19 |

| 2.8  | SEGV handler for page $p$                                                                           | 20 |

| 2.9  | Diff Creation                                                                                       | 21 |

| 2.10 | Combining diff requests $(x, y, z \text{ all on page } p) \dots \dots \dots \dots \dots$            | 21 |

| 2.11 | Lock Acquisition                                                                                    | 22 |

| 2.12 | Lock Request Handler                                                                                | 23 |

| 2.13 | Lock Release                                                                                        | 23 |

| 2.14 | False Sharing                                                                                       | 24 |

| 2.15 | Multiple Writers: X,Y on same page                                                                  | 25 |

| 2.16 | Bad diff combine: $x, y$ same page $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 27 |

| 2.17 | Hybrid Barrier Flush                                                                                | 29 |

| 2.18 | RC Page State Transitions                                                                           | 31 |

| 3.1  | Parallel Linkage Computation                                                                        | 41 |

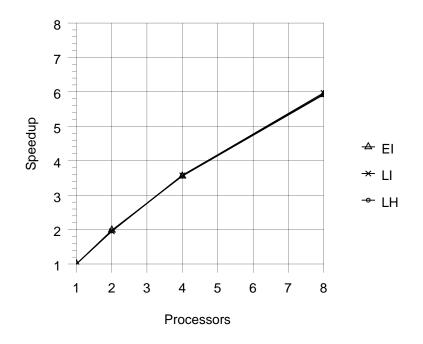

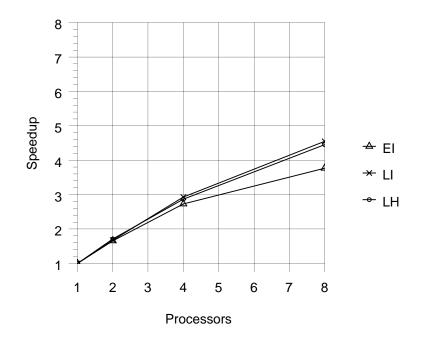

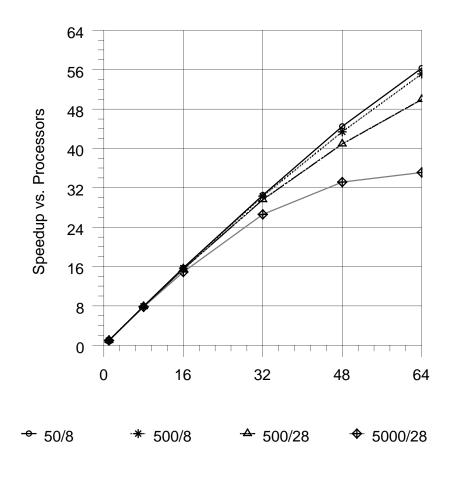

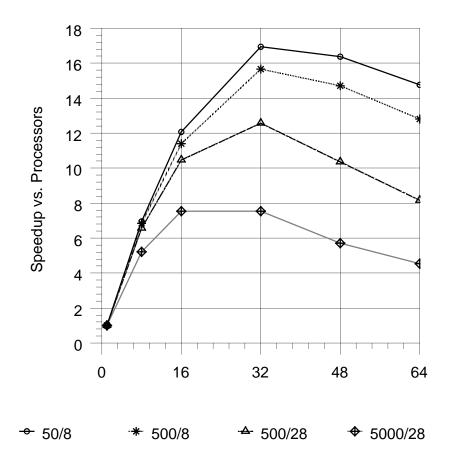

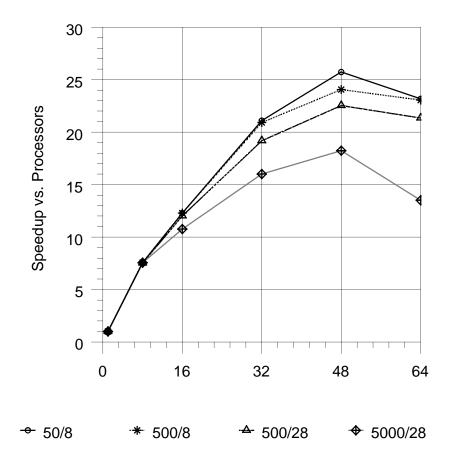

| 3.2  | Speedups for Barnes Hut                                                                             | 46 |

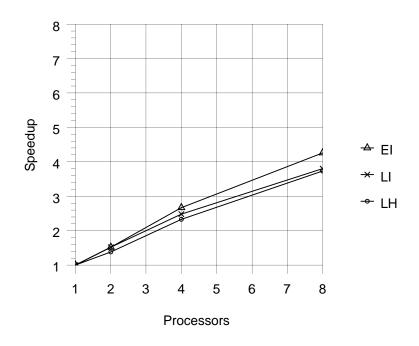

| 3.3  | Speedups for FFT                                                                                    | 47 |

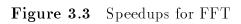

| 3.4  | Speedup for ILINK                                                                                   | 47 |

| 3.5  | Speedups for IS                                                                                     | 48 |

| 3.6  | Speedups for MIP                                                                                    | 48 |

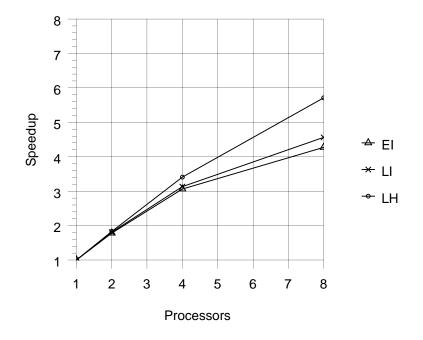

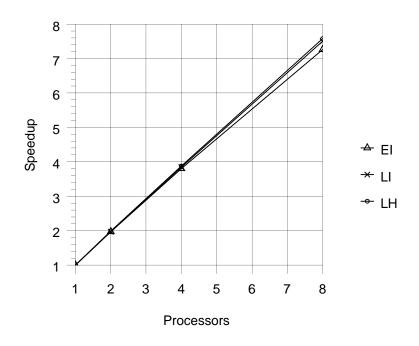

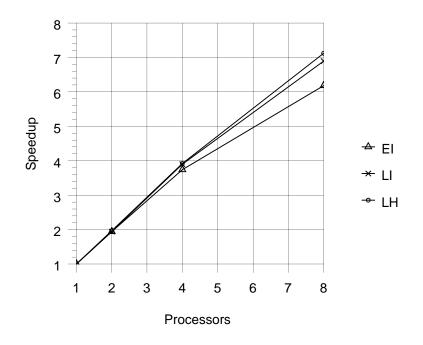

| 3.7  | Speedups for SOR                               |

|------|------------------------------------------------|

| 3.8  | Speedups for TSP                               |

| 3.9  | Speedups for Water                             |

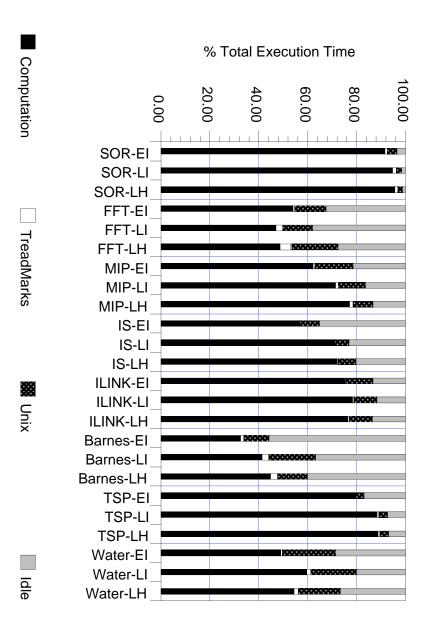

| 3.10 | TreadMarks Execution Time Breakdown            |

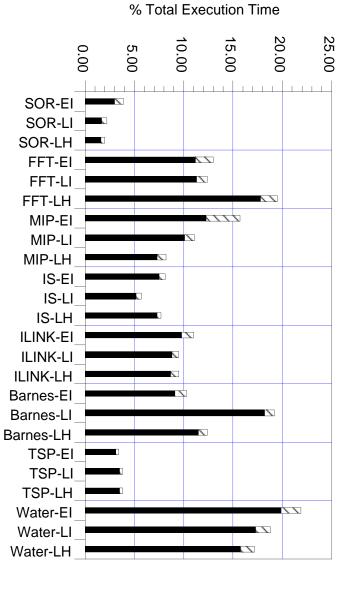

| 3.11 | Unix Overhead Breakdown                        |

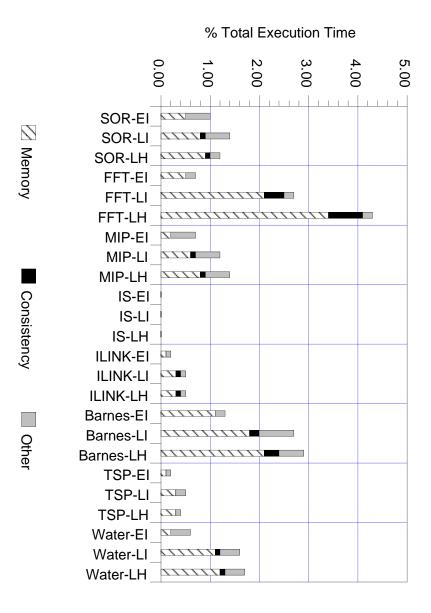

| 3.12 | TreadMarks Overhead Breakdown                  |

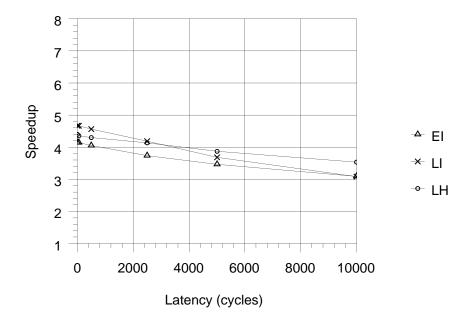

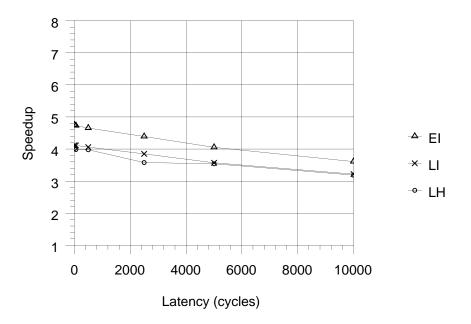

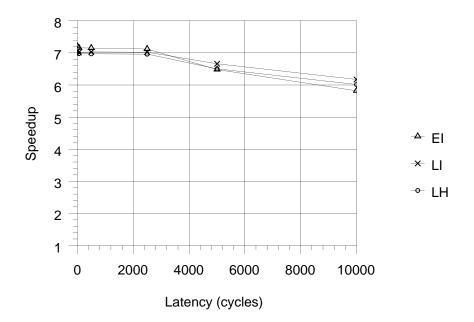

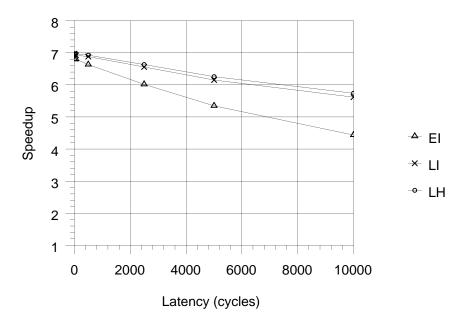

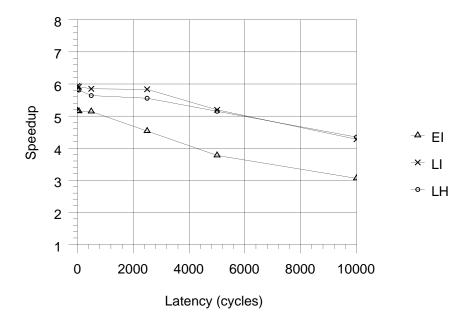

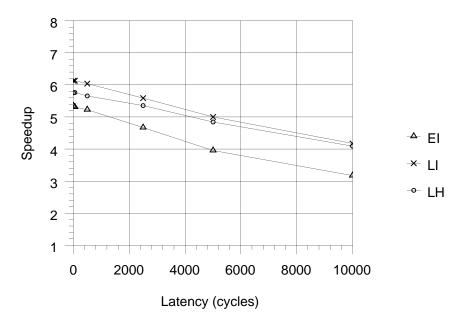

| 3.13 | Barnes: Varying Fixed Message Cost             |

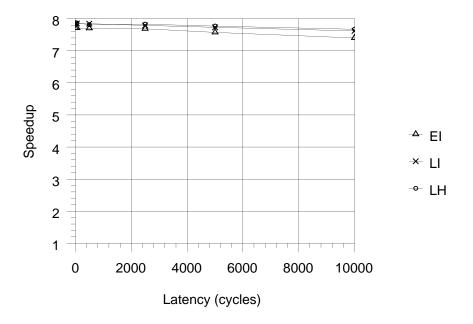

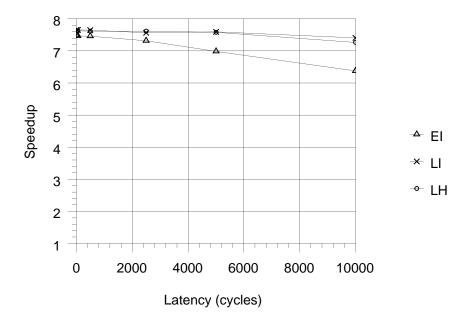

| 3.14 | FFT: Varying Fixed Message Cost                |

| 3.15 | ILINK: Varying Fixed Message Cost              |

| 3.16 | IS: Varying Fixed Message Cost                 |

| 3.17 | MIP: Varying Fixed Message Cost                |

| 3.18 | SOR: Varying Fixed Message Cost                |

| 3.19 | TSP: Varying Fixed Message Cost                |

| 3.20 | Water: Varying Fixed Message Cost              |

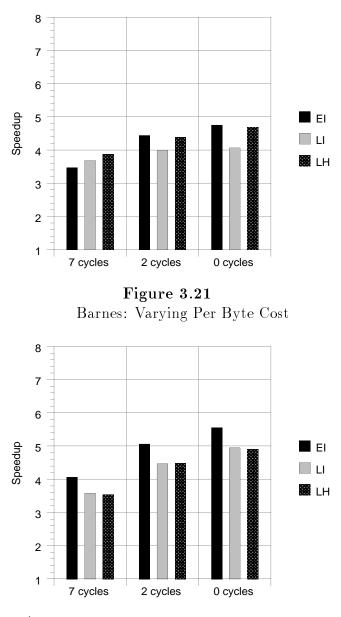

| 3.21 | Barnes: Varying Per Byte Cost                  |

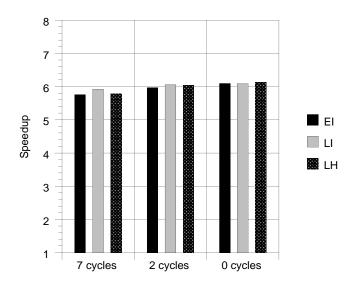

| 3.22 | FFT: Varying Per Byte Cost                     |

| 3.23 | ILINK: Varying Per Byte Cost                   |

| 3.24 | IS: Varying Per Byte Cost                      |

| 3.25 | MIP: Varying Per Byte Cost                     |

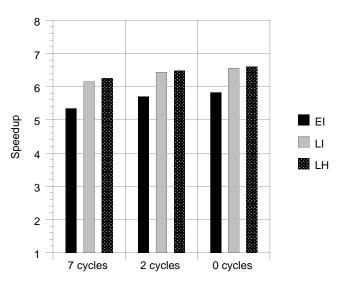

| 3.26 | SOR: Varying Per Byte Cost                     |

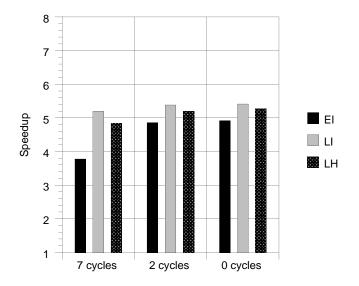

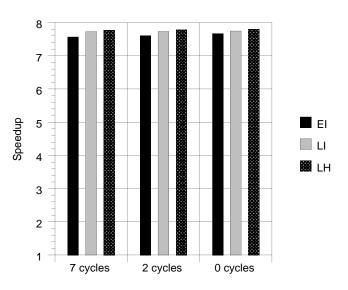

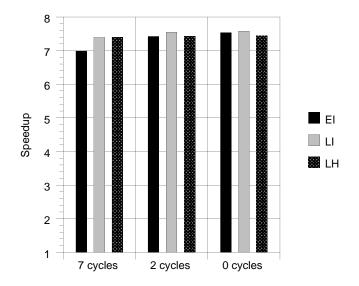

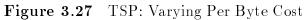

| 3.27 | TSP: Varying Per Byte Cost                     |

| 3.28 | Water: Varying Per Byte Cost                   |

| 3.29 | Barnes Hut: Varying Bandwidth                  |

| 3.30 | FFT: Varying Bandwidth 72                      |

| 3.31 | ILINK: Varying Bandwidth                       |

| 3.32 | IS: Varying Bandwidth                          |

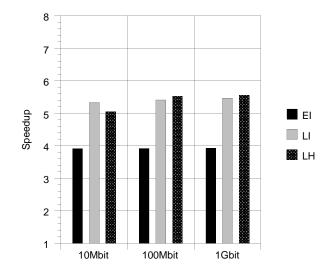

| 3.33 | MIP: Varying Bandwidth                         |

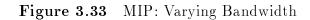

| 3.34 | SOR: Varying Bandwidth                         |

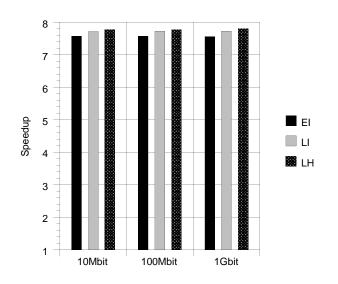

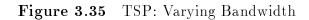

| 3.35 | TSP: Varying Bandwidth                         |

| 3.36 | Water: Varying Bandwidth                       |

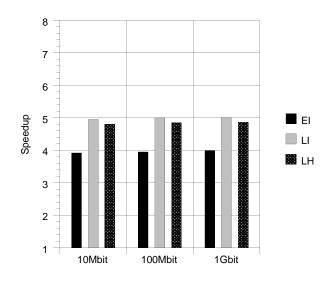

| 4.1  | 8-Processor Speedup: TreadMarks vs. SGI 4D/480 |

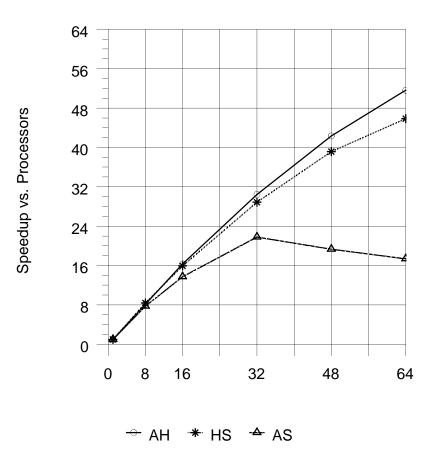

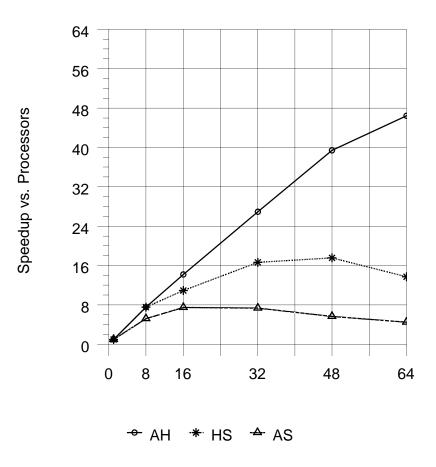

| 4.2  | Speedups for SOR: $2000 \times 1000$           |

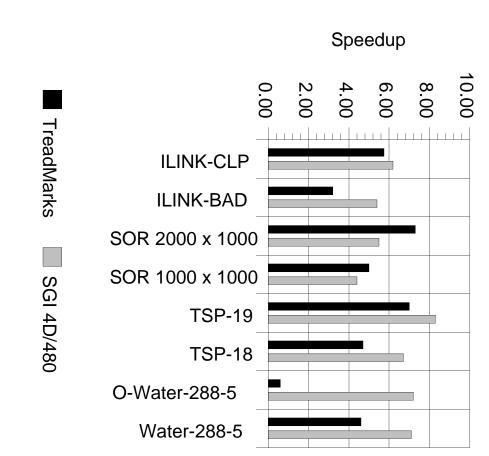

| 4.3  | Speedups for TSP: 19 Cities                    |

| 4.4 | Speedups for Water: 288 Molecules and 2 Steps             | 88 |

|-----|-----------------------------------------------------------|----|

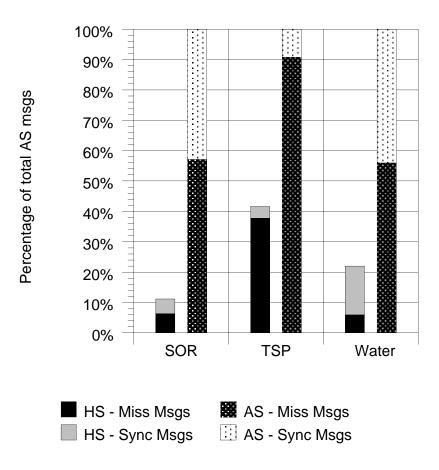

| 4.5 | Total Messages                                            | 89 |

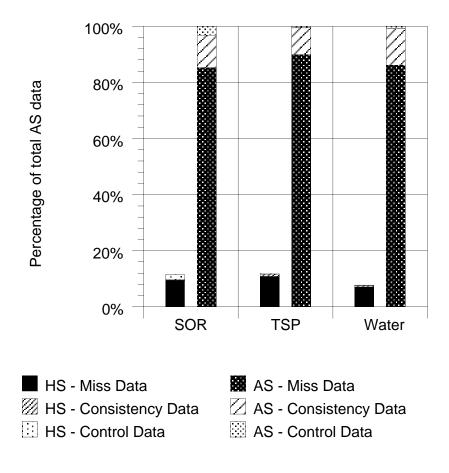

| 4.6 | Total Data                                                | 90 |

| 4.7 | AS Speedups for SOR: 2000 $\times$ 1000 $\hdots$          | 91 |

| 4.8 | AS Speedups for Water: 288 Molecules and 2 Steps          | 92 |

| 4.9 | HS Speedups for Water: 288 Molecules and 2 Steps $\ldots$ | 93 |

# Tables

| 2.1 | Shared Memory Operation Message Costs | 35 |

|-----|---------------------------------------|----|

| 2.2 | Protocol Tradeoffs                    | 36 |

| 3.1 | Cost of sending messages              | 39 |

| 3.2 | Application Suite                     | 45 |

| 3.3 | Lazy and Eager Rate Statistics        | 51 |

| 3.4 | Protocol Tradeoffs                    | 60 |

| 4.1 | TreadMarks vs. SGI $4D/480$           | 78 |

| 4.2 | Real and Simulated Speedups           | 84 |

## Chapter 1

## Introduction

The current trend in the supercomputer industry is to build parallel machines using off-the-shelf processors and a high-performance interconnect. The primary reason for this is that off-the-shelf microprocessors are now nearly as fast as the best custom chip sets. A relatively small number of these microprocessors linked together by a highperformance interconnect can provide a shared address space and very high aggregate performance. Moreover, using commonly available microprocessors provides a clear upgrade path as new processors are produced.

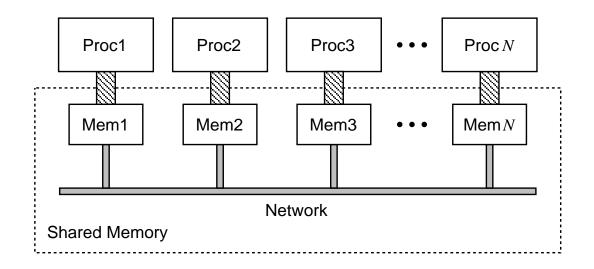

As a result of these trends, the same processors used in supercomputers are often used in ordinary workstations on local area networks. Supporting the abstraction of shared memory on these high-performance *multicomputers* is an obvious idea. However, local area networks have historically lacked the high bandwidth and low latency of supercomputer interconnects, as well as the hardware support for implementing shared memory over the message-passing interconnect. Conventional wisdom therefore says that distributed shared memory (DSM) systems, which provide shared address spaces to networks of workstations (see Figure 1.1), can not be implemented efficiently.

This thesis develops a family of *lazy release consistent* (LRC) protocols that effectively address many of the problems inherent in supporting DSM on a network. LRC protocols delay communicating consistency information until absolutely required to do so by the memory model. At the other end of the spectrum are *eager* protocols, which attempt to minimize latency by optimistically moving data before it is actually needed. By moving data and consistency information only upon request, the lazy protocols often require significantly less communication than eager protocols. The primary drawback of this approach is that hiding communication latency by overlapping communication with computation becomes more difficult. However, we have found that for many classes of programs, the reduction in message traffic achieved by the lazy protocols more than offsets any added latency.

Figure 1.1 Distributed Shared Memory

The LRC protocols have been implemented on a network of eight workstations, and timing information from the implementations has been used to calibrate simulations of up to 64-processor clusters of workstations. Our results show that efficiently supporting the abstraction of shared memory in software is possible for a broad class of applications, but only with the use of high-performance protocols that are specifically crafted to reduce communication requirements. Given appropriate protocols, DSM systems can have performance comparable to hardware systems [LT88] for small clusters, and significant speedup even on large clusters.

## 1.1 Programming Model

The LRC protocols developed in this work provide a generic abstraction of shared memory to application programs. Programs are multi-threaded, and synchronize through locks and barriers. All data communication between threads is through globally shared memory. For most programs, the memory abstraction supported by LRC protocols is indistinguishable from that of a multiprocessor that supports shared memory in hardware [LT88].

The protocols and the system described in this dissertation do not require user annotation or language support. For several reasons, we feel that it is important for DSM systems to transparently run programs written for hardware shared memory systems. First, the overriding rationale for using DSM systems is that they are easier to use than message-passing systems. DSMs handle data movement automatically, while message-passing systems require data movement to be specified by the programmer. Requiring users to annotate shared variables or sharing patterns may negate the underlying rationale of DSMs.

Second, we believe that low-level customization hooks can and should allow experienced users to tune system performance. However, requiring all programmers to reason about the underlying implementation would likely be counterproductive.

Finally, none of the work described in this thesis disallows later addition of application-specific semantic information. In fact, most such optimizations are orthogonal to the decisions made in this thesis. Beginning without any applicationspecific information forces us to reason clearly about general application characteristics, and to identify and address common sharing patterns. Once general-purpose mechanisms that efficiently support large classes of applications are in place, specialpurpose mechanisms that exploit application-specific information can be added to bring the performance as close to optimal as possible.

### 1.2 Challenges

The following paragraphs describe the two primary obstacles to obtaining good performance on a software implementation of distributed shared memory.

#### Communication

The high cost of communication on local area networks can hurt performance in two ways. First, large amounts of communication can cause the network to become a bottleneck. Historically, network multicomputers have had less bandwidth and higher latency than hardware shared memory (HSM) machines. However, the ATM networks used by our implementation and modeled in the simulations are fast enough that the actual *wire time* of messages is always dwarfed by operating system costs.

More important on our target systems is the *software overhead* incurred any time a message is sent or received. Each message send, for example, requires traversing many different levels of system software from the kernel trap down to the network interface, often making the actual wire time an insignificant contributor to the overall transmission cost. Lazy protocols are ideally suited for situations where communication has a high per message cost, because they send messages only when absolutely necessary, often resulting in far fewer messages overall.

## False Sharing

False sharing results when the system can not distinguish between accesses to logically distinct pieces of data. False sharing occurs because the system tracks accesses at a granularity larger than the size of individual shared data items. Conventional protocols typically require processes to gain sole access to a page before it can be modified. Therefore, false sharing can lead to situations where multiple processes contest ownership of a page, even though the processes are modifying entirely disjoint sets of data. The page may then "ping-pong" back and forth between the processes.

The LRC protocols presented in this thesis allow processes to modify pages without gaining sole ownership of a page. Multiple processes can thereby modify falsely shared data simultaneously, without network communication. False sharing is more common on DSM systems than on HSM systems because DSMs track accesses at the granularity of virtual memory pages, while HSMs track accesses at the granularity of cache lines.

### 1.3 Lazy Release Consistency

Lazy release consistency is based on release consistency (RC) [GLL+90], a relaxed memory consistency model that permits a processor to delay making its changes to shared data visible to other processors until subsequent synchronization accesses occur. Essentially, all shared accesses are divided into ordinary accesses, acquire synchronization accesses, and release synchronization accesses. Release consistency allows the results of ordinary shared writes to be buffered locally until the next release operation.

In contrast, sequential consistency (SC) [Lam79], until recently the model implemented by most bus-based multiprocessors, requires all prior shared writes to complete before any subsequent shared accesses can be initiated. RC systems can achieve large performance gains over SC systems because they allow updates to be buffered.

The primary disadvantage of using RC is that the memory abstraction seen by the user is slightly different than with SC. However, programs written for SC produce the same results on an RC memory, provided that (i) all synchronization operations use system-visible primitives, and (ii) there is a chain of synchronization between every pair of conflicting ordinary accesses to the same memory location by different processors [GLL+90]. In practice, most shared memory programs require little or no modification to meet these requirements.

LRC is a refinement of RC that allows consistency action to be postponed until a synchronization variable released in a subsequent operation is acquired by another processor. Even then, the shared writes are made visible only to the acquiring processor. Synchronization transfers in an LRC system, therefore, involve only the synchronizing processors. A release in an eager RC system requires the releasing processor to make its shared writes visible to all other processors in the system that cache the data. This reduction in synchronization traffic can result in a significant decrease in the total amount of system communication, and a consequent increase in overall performance.

## 1.4 Thesis

This dissertation centers around the following three claims:

**Claim 1.1** DSM systems based on LRC require less communication than systems based on comparable eager protocols.

Earlier work has shown that eager release consistent (ERC) systems outperform conventional DSM systems and can approach explicit message passing in communication requirements [Car93]. We therefore use ERC protocols as the yardstick with which to gauge the success of the LRC protocols.

LRC protocols piggyback consistency information on top of synchronization messages, and only move data when needed. Eager protocols attempt to hide communication latency by moving data ahead of any need. Our work shows that for a broad class of systems, the extra communication needed to move data eagerly overshadows any gains made in hiding latency.

Claim 1.2 DSM systems based on LRC can achieve better performance on a broader range of applications than systems based on eager protocols.

Many previous systems either restricted their focus to coarse-grained programs [LH89, FP89], required user annotations [ZSB94, Lee94], or substantially changed the programming model [BT88, DCM<sup>+</sup>90]. Each of these choices has merit, but none of them is ideal from the standpoint of transparently handling a broad range of programs. LRC protocols can efficiently handle complicated sharing patterns and data layouts without user annotations or changes in the programming model because they reduce the communication impact of synchronization operations. Hence, LRC allows a broader range of existing programs to be run efficiently.

**Claim 1.3** DSM systems can often obtain performance competitive with hardware shared memory systems.

Claim 1.3 has been made before, but this work supersedes previous work in that (i) we show that the lazy protocols usually perform substantially better than the eager protocol [DKCZ93, Car93] that represents the previous state of the art, and (ii) we back up our contention by presenting a detailed performance comparison of our system with a hardware shared memory system that is based on the same processors and caches, as well as extensive simulations.

## 1.5 Contributions

The primary contributions of this dissertation are the design, implementation, and evaluation of the LRC protocols, and the consequent validation of the claims made in Section 1.4.

Claim 1.1 says LRC systems require less communication than ERC systems. In order to validate this contention, we extensively simulated several variants of each type of system, and then built TreadMarks and analyzed its performance. TreadMarks is an LRC-based DSM system that runs on standard workstations and operating systems.

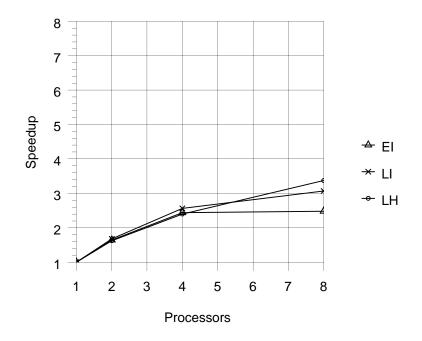

We also built eager versions of TreadMarks, and analyzed differences in performance and communication behavior between the variants. Our results show that there is little difference between lazy and eager systems for coarse-grained programs, but the difference grows substantially as the programs become more fine-grained, either in synchronization or in data sharing. Seven of the eight applications in our suite performed better on the LRC system than on the eager, and four of those programs performed at least 18% better. Although there are certainly classes of programs for which eager protocols would require less communication than LRC protocols, none of our programs displayed this behavior.

Claim 1.2 contends that LRC protocols can efficiently execute a broader range of programs than eager systems. Our application suite includes a wide variety of programs drawn from several different sources. The programs range from fine-grained lock-based programs to coarse-grained programs that use only barriers. The results of Chapter 3 show that, with one exception, the LRC protocols consistently outperform the eager protocols over all combinations of sharing and synchronization patterns.

Finally, Claim 1.3 makes the controversial contention that DSM systems can perform comparably to hardware-based systems. Our defense of this claim rests on two studies.

The first is a comparison of the performance of TreadMarks to that of a SGI shared memory machine that uses the same processors, primary caches, and compiler as the machines running TreadMarks. The primary difference between the two systems is the way the shared memory abstraction was implemented. Our results show that TreadMarks performs better than the SGI for one program, and nearly as well for several others. However, the SGI performs substantially better for the most finegrained programs.

The second experiment was a simulation study driven by numbers from the implementations. We were able to confirm our conclusions from the performance study and pinpoint where such factors as network bandwidth become a limiting factor in achieving good performance for software systems.

Additionally, we investigated hybrid systems that used hardware shared memory in small-scale clusters, and software DSM in between clusters. Our results show that software system performance drops off rapidly as system size increases. However, hybrid systems can run coarse and medium-grained programs nearly as fast as hardware for up to 64 processes. The fine-grained programs performed little better on the hybrid system than on the software system, primarily because synchronization accesses usually require network communication in either case.

## Chapter 2

## Lazy Release Consistency

We describe the LRC memory model and present a qualitative argument arguing that protocols implementing LRC require less communication, and hence achieve better performance, than protocols implementing other memory models. We then present the design and implementation of three software DSM protocols: lazy invalidate (LI), lazy hybrid (LH), and eager invalidate (EI). LI and LH are new protocols that implement LRC. EI is a straightforward, invalidate-based implementation of eager release consistency (See Section 2.3.3). EI is used as the basis for our comparisons in Chapter 3 because studies [CBZ91, Car93] have shown that eager update protocols uniformly perform better than conventional protocols, and our own work [KCZ92, DKCZ93] has shown that eager invalidate protocols outperform eager update protocols.

Section 2.1 describes the user interface of TreadMarks, the DSM system in which all three protocols are implemented. Section 2.3 describes the design and implementation of the three protocols. Section 2.4 presents a proof that LRC is indistinguishable from conventional memory models under most conditions, and Section 2.5 summarizes the chapter.

## 2.1 Application Program Interface (API)

TreadMarks is entirely implemented as a C library, using an interface similar to the parmacs macros from Argonne National Laboratory [Lea87] for process and synchronization support. While the parmacs macros are implemented using m4 macros, our DSM library is implemented as a set of procedure calls. Nonetheless, properly synchronized programs using the parmacs macros can be ported to our system with only minor changes in naming and initialization.

TreadMarks programs follow a conventional shared memory style, using processes to express parallelism, and locks and barriers to synchronize. Typically, the *manager*  process initializes the DSM system, allocates and initializes shared memory, and then starts a single remote process on each remote processor via Tmk\_startup.

The manager process passes the address of the shared region to other processes through a Tmk\_distribute call. After initialization is complete, the parent and children each perform a portion of the work, communicating only through synchronization operations (Tmk\_lock\_acquire and Tmk\_lock\_release, Tmk\_barrier).

The Figure 2.1 shows a complete, runnable program that fills an array in parallel.

## 2.2 Lazy Release Consistency

### 2.2.1 Motivation and Background

Most previous DSM systems supported the canonical consistency model, *sequential* consistency (SC) [Lam79]. However, many studies have shown that sequential consistency poses serious problems for efficient distributed implementations of shared memory, primarily because sequential consistency imposes such strict requirements on system-wide ordering of accesses to shared memory [Adv93]. Sequential consistency is defined as follows:

#### Definition 2.1 Sequential Consistency

A system is *sequentially consistent* if the result of any execution is the same as if the operations of all the processors were executed in some sequential order, and the operations of each individual processor appear in this sequence in the order specified by its program.

This definition can be paraphrased as requiring all shared accesses to be consistent with some total ordering, such that this total ordering does not violate program order. SC does not require an implementation to actually establish a total ordering on all accesses, but it does require all reads to return values that are consistent with such an ordering. For instance, Figure 2.2 shows an execution that violates SC, assuming each operation occurs atomically and program order is respected.  $P_1$  and  $P_2$  disagree on the ordering of the writes.  $P_1$  can only conclude that  $w_1 \prec r_1 \prec w_2 \prec r_2$ , while  $P_2$ concludes  $w_2 \prec r_2 \prec w_1 \prec r_1$ . Figure 2.3, on the other hand, is a valid sequentially consistent result because both processes can agree on an ordering that is consistent with the returned values.

```

/*

* File app.c

*/

#include "Tmk.h"

extern char

*optarg;

arrayDim = 100;

int

int

*array;

void main(int argc, char **argv)

{

c, start, end, i;

int

while ((c = getopt(argc, argv, "d:")) != -1)

switch (c) {

case 'd':

arrayDim = atoi(optarg);

break;

}

Tmk_startup(argc, argv);

if (Tmk_proc_id == 0) {

array = (int *) Tmk_malloc(arrayDim * sizeof(int));

Tmk_distribute(&array, sizeof(array)); /* Send 4-byte ptr value */

}

Tmk_barrier(0);

start = Tmk_proc_id * (arrayDim / Tmk_nprocs);

end = (Tmk_proc_id + 1) * (arrayDim / Tmk_nprocs);

if (end > arrayDim) end = arrayDim;

for (i = start; i < end; i++)</pre>

array[i] = i;

Tmk_barrier(0);

Tmk_exit(0);

}

```

$\begin{array}{ccc} \mathbf{P_1} & \mathbf{P_2} \\ w_1(x)2 & w_2(y)2 \\ r_1(y)0 & r_2(x)0 \end{array}$

**Figure 2.2** Not SC (x, y initially zero)

$\begin{array}{ccc} {\bf P_1} & {\bf P_2} \\ w_1(x)2 & w_2(y)2 \\ r_1(y)0 & r_2(x)2 \end{array}$

**Figure 2.3** SC (x, y initially zero)

While useful as a description of a base memory model, sequential consistency is no longer commonly used in new parallel machines. Many hardware optimizations that are used to hide memory access latency violate SC. For instance, the example in Figure 2.2 could be produced by a machine that has write buffers, and allows reads to bypass writes in the buffers.

Supporting SC in the presence of non-atomic memory transactions is even more difficult. An update in a distributed system can be logically decomposed into a series of sub-operations [Col91], each of which applies to a single process. If the relative orderings of sub-operations of competing memory operations do not agree, then SC is violated. This problem is especially severe in systems in which sub-operations take differing amounts of time to complete, such as ring architectures that support concurrent access [WHL92], or NUMA machines [BSF+91, SJG92, BFS89, Cox92, CF89, LE91, LEK91].

### 2.2.2 Release Consistency

Release consistency (RC) [GLL+90], hereafter referred to as *eager* release consistency, is a *relaxed* memory consistency model that permits a process to delay making its changes to shared data visible to other processes until certain synchronization accesses occur. At an intuitive level, RC allows views of shared memory by different processes to become inconsistent until subsequent synchronization events.

A useful memory model must effectively address ease of use as well as performance. Relaxed consistency models are attractive because they allow better performance than previous models. However, if the resulting programming model is non-intuitive, the lack of programming effectiveness offsets any gains in performance.

Eager release consistency addresses the performance issue by allowing write accesses to be pipelined or batched, and addresses the programming model issue by guaranteeing results equivalent to an SC system for *properly-labeled* [GLL+90] programs. Informally, a program is properly-labeled if the program contains enough synchronization to avoid data races. This concept is similar to the notion of *datarace-free*, which will be discussed in Section 2.2.4.

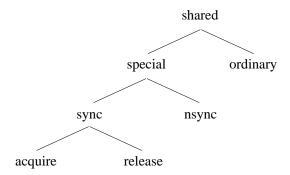

Figure 2.4 shows how RC categorizes shared memory accesses. In order to explain this categorization, we first explain the notion of *competing accesses*. Two shared accesses by different processes *compete* if they apply to the same location and at least one is a write. Sync accesses are competing accesses used to enforce ordering or atomicity among multiple processes. Nsync accesses are competing accesses that do not enforce orderings, such as competing accesses to neighbor data in chaotic relaxation algorithms. Sync accesses are further divided into acquires and releases, acquires being used to gain access to shared data, and releases being used to grant such accesses. Ordinary accesses are those that do not compete in executions of properly labeled programs.

#### Definition 2.2 Conditions for Eager Release Consistency

(A) Before an ordinary read or write access is allowed to perform with respect to any other process, all previous acquire accesses must be performed, and

(B) before a **release** access is allowed to perform with respect to any

Figure 2.4 Categorization of Writable Accesses

other process, all previous ordinary **read** and **store** accesses must be performed, and

(C) sync accesses are sequentially consistent with respect to one another.

Informally, a shared access is *performed* at a process when its result is visible at the process. Acquires and releases may be thought of as conventional synchronization operations on a lock, or P's and V's on binary semaphores, but other synchronization mechanisms can be expressed as well. For instance, the arrival of a worker process at a barrier can be modeled as a release by the worker followed by an acquire by the manager, and departure of a worker from a barrier can be modeled as a release by the worker. Essentially, RC requires ordinary shared memory updates by a process p to become visible at other processes only when a subsequent release by p becomes visible at another process, q.

### 2.2.3 Lazy Release Consistency

While eager release consistency allows quite a bit of latitude in deciding when to perform ordinary shared accesses, it still requires accesses to be performed globally before a local **release** can complete. Lazy release consistency is a refinement of eager release consistency that allows synchronization transfers to take place without performing any ordinary shared accesses globally. Instead, the shared accesses only have to be performed at other processes as they synchronize with the performing process.

### Definition 2.3 Conditions for Lazy Release Consistency

(A) Before an ordinary read or write access is allowed to perform with respect to another process, all previous acquire accesses must be performed with respect to that other process, and

(B) before a **release** access is allowed to perform with respect to any other process, all previous ordinary **read** and **store** accesses must be performed with respect to that other process, and

(C) sync are sequentially consistent with respect to one another.

Definition 2.2 requires ordinary accesses to be performed globally at the next release, whereas Definition 2.3 requires only that ordinary accesses be performed with respect to other processes as subsequent releases become visible to them.

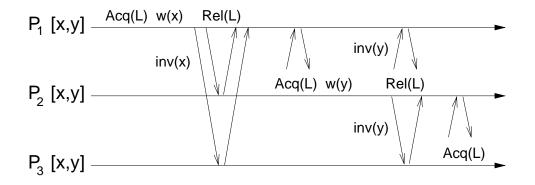

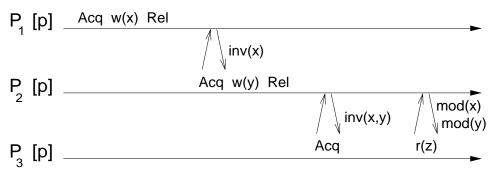

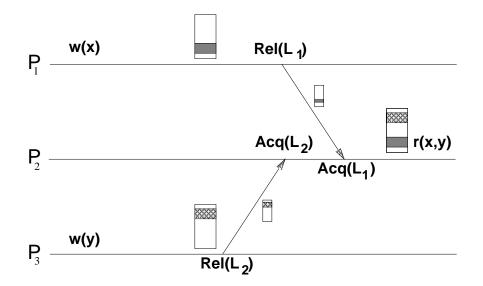

Figure 2.5 shows three processes exchanging synchronization in an eager release consistent DSM using an invalidate protocol. Each process caches pages x and y. Process  $P_1$  modifies page x and then releases a synchronization variable. At this point, Definition 2.2 requires that all previous ordinary accesses, the write to page x in this case, be performed everywhere in the system. For an invalidate protocol, "performing" a write means invalidating other copies, so invalidate messages are sent to all other processes that cache x. When  $P_2$  likewise modifies page y and performs a release, invalidate messages must again be sent to all other processes that cache the affected page.

Unnecessary communication takes place at two levels in this example. First, all three invalidation messages are useless in the sense that the targets of the invalidations never access the invalidated data, and hence would not notice if their copies became inconsistent. Second, the invalidation of x to  $P_2$  travels the same route as a subsequent lock transfer, so a pair of messages could be eliminated by piggybacking the invalidation to the synchronization transfer.

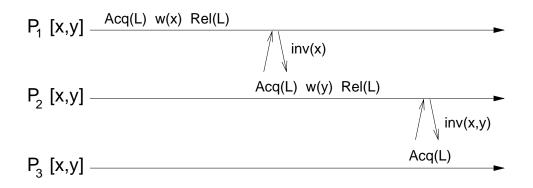

Figure 2.6 shows the same example under an LRC invalidate protocol. Consistency management is moved from releases to subsequent acquires, and invalidates are sent only to the acquiring process. Even more importantly, LRC is able to combine the invalidation and the synchronization transfer into a single message pair because they occur at the same time.

This simple example shows some of LRC's considerable potential to reduce communication requirements over that needed by ERC. Eager systems flush modifications globally prior to releases, but lazy systems only pass consistency information between

Figure 2.5 Eager Release Consistency

Figure 2.6 Lazy Release Consistency

processes that synchronize with each other. LRC systems therefore need to maintain transitive information. In Figure 2.6, the lock grant from  $P_2$  to  $P_3$  not only carries an invalidation for y, which was modified by  $P_2$ , but also an invalidation for x, which was previously modified by  $P_1$ .

#### 2.2.4 Happened-Before-1

In order to support the memory model described in Definition 2.3, we use a *happened-before-1* [AH93] partial ordering over all shared accesses:

**Definition 2.4** Shared memory accesses are partially ordered by *happenedbefore-1*, denoted  $\xrightarrow{hb1}$ , defined as follows:

- If  $a_1$  and  $a_2$  are accesses on the same process, and  $a_1$  occurs before  $a_2$  in program order, then  $a_1 \xrightarrow{\text{hb1}} a_2$ .

- If  $a_1$  is a release on process  $p_1$ , and  $a_2$  is an acquire on the same memory location on process  $p_2$ , and  $a_2$  returns the value written by  $a_1$ , then  $a_1 \xrightarrow{\text{hb1}} a_2$ .

- If  $a_1 \xrightarrow{\text{hb1}} a_2$  and  $a_2 \xrightarrow{\text{hb1}} a_3$ , then  $a_1 \xrightarrow{\text{hb1}} a_3$ .

The happened-before-1 relation is the transitive closure of program order and synchronization order (i.e. an acquire is ordered after the last previous release of the same synchronization variable).

LRC requires that before a process may continue past an acquire, all shared accesses that precede the acquire according to  $\xrightarrow{hb1}$  must be performed at the acquiring

process, where "performing" an access at process p means either updating or invalidating p's copy of the indicated data item.

LRC protocols guarantee to support the same programming model as sequentially consistent protocols if programs are *data-race-free*. The following definitions are from Adve [AH93]:

**Definition 2.5** A *data race* in an execution is a pair of conflicting operations, at least one of which is to data, that is not ordered by the happened-before-1 relation defined for the execution. An execution is *data-race-free* if and only if it does not have any data races. A program is *data-race-free* if and only if all its sequentially consistent executions are data-race-free.

Data-race-free programs produce the same results on LRC systems as they do on sequentially consistent systems. This requirement is usually not as arduous as it may seem, because many (if not most) parallel programs are data-race-free already. Some classes of algorithms, such as chaotic algorithms, can tolerate temporary inconsistencies in their shared data. Otherwise, a data race usually represents a bug.

While satisfying Definition 2.4 is by itself enough to satisfy LRC, maintaining and using such a detailed ordering on individual shared accesses would be prohibitively expensive. Instead, the lazy protocols generalize the ordering to apply to process *intervals*. Intervals are segments of time in the execution of a single process. New intervals begin each time a synchronization access is executed by the process. We define the *happened-before-1* partial order between intervals in the obvious way: an interval  $i_1$  precedes an interval  $i_2$  according to  $\xrightarrow{\text{hb1}}$ , if all accesses in  $i_1$  precede all accesses in  $i_2$  according to  $\xrightarrow{\text{hb1}}$ . An interval is said to be performed at a process if all the interval's accesses have been performed at that process.

The lazy protocols track which intervals have been performed at a process by maintaining a per process vector timestamp [Mat89]. A vector timestamp consists of a set of interval indices, one per process in the system. Let  $vv_p^i$  be the vector timestamp of process p at interval i. The entry for process  $q \neq p$ , denoted  $vv_p^i[q]$ , specifies the most recent interval of process q that has been performed at process p. Entry  $vv_p^i[p]$  is equal to i.

Interval  $\sigma_q^x$ , or interval x of processor q, is termed *covered* by  $vv_p^i$  if  $vv_p^i[q]$  is greater than or equal to x. We also use the notation  $\epsilon$  to represent *covered*.

The lazy protocols pass consistency information in the form of write notices that are attached to intervals. A write notice is an indication that a given page has been modified. Each interval contains a write notice for every page that was modified during the segment of time corresponding to the interval. Write notices are used in the **send\_set**, which is the set of all write notices created during intervals that have been performed at the releasing process, but not at the acquiring process. If  $vv_r^i$ is the vector timestamp of a release process and  $vv_a^j$  is the vector timestamp of the corresponding acquire process, then the **send\_set** consists of all intervals  $\sigma_p^x$ , such that  $\sigma_p^x \epsilon vv_r^i$  and not  $\sigma_p^x \epsilon vv_a^j$ . In order to create the **send\_set**, vector timestamps are included on synchronization requests.

### 2.3 Protocols

A TreadMarks program consists of one or more processes communicating through sockets. In order to minimize the demands on the underlying operating system, we do not expect lightweight process support and therefore run only a single process on each machine.

At system startup, library routines create the requested number of processes on other machines, set up fully connected sockets between the processes, and register a SIGIO handler to handle incoming requests asynchronously. Each process allocates a large block of local memory to use as the shared mapping of the virtually shared memory. The block is located at the same address on each machine. For each page of this memory, a "manager" processor is designated.

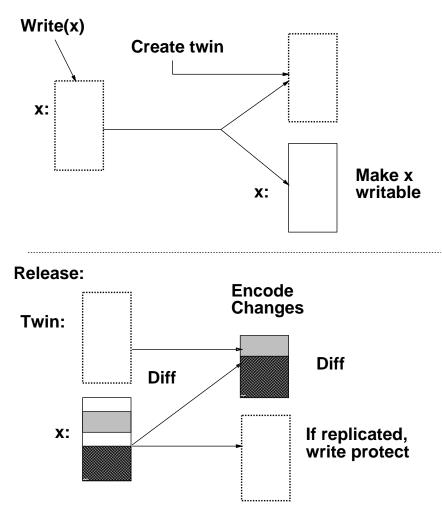

A SEGV handler is registered with the operating system in order to detect and intercept write accesses to shared pages. The SEGV handler is called when a process tries to access data on an unmapped or protected page. The handler retrieves a valid copy of the page from the manager, adds read permission to the page, and allows the access to proceed. The SEGV handler is also called when a write access to a valid page is first performed. The handler creates a *twin*, or copy, of the page, and stores it in system space. A comparison of the twin and a later version of the page is used to create a *diff*, which is a run-length encoding of the differences between the two versions. The diff can then be used to update other processes' copies of the page. With the exception of the first time a processor accesses a page, a processor's version of a given page is updated exclusively by applying diffs; a new complete copy of the page is never needed. The only strictly necessary service that a DSM needs to provide is a coherent view of shared memory. However, synchronizing through software-supported shared memory can be unreasonably slow. We therefore separate synchronization mechanisms from ordinary shared memory mechanisms. The advantages gained thereby are twofold: (i) better performance for synchronization, and (ii) the opportunity to tune shared memory consistency mechanisms to application-level synchronization (i.e. release consistency).

#### 2.3.1 Lazy Invalidate

#### Pages and Data

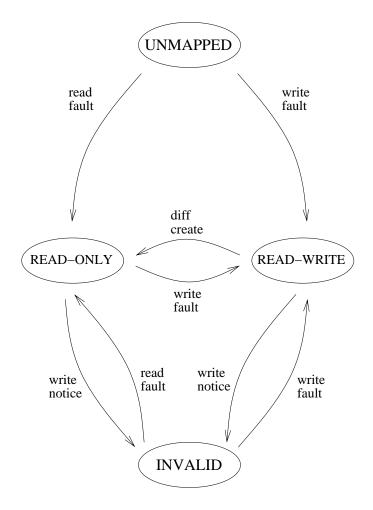

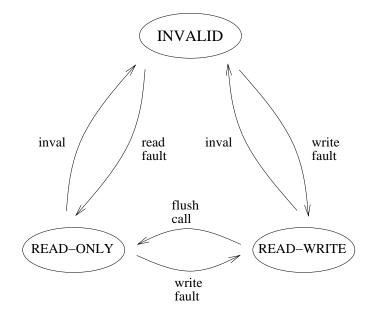

Shared pages each have a statically assigned manager. As indicated in Figure 2.7, they have four possible states: UNMAPPED, INVALID, READ\_ONLY, and READ\_WRITE. At startup, all shared pages of a given processor that are not owned by that processor are in an UNMAPPED state.

There are three types of page faults that can occur: a *cold miss*, which occurs the first time a page is accessed by a processor that is not the manager, a *coherence miss*, which occurs when a page is accessed after it has been invalidated due to coherence actions, and a *protection fault*, which occurs when a write access occurs to a valid but READ\_ONLY page. Pseudo-code for the SEGV handler, which handles all three types of faults, is shown in Figure 2.8.

On a *cold miss*, a copy of the page is retrieved from the manager and put into a READ\_ONLY state. It does not matter whether the manager or other processors have modified the page or not.

In response to a protection fault, the SEGV handler changes the virtual memory page's state to READ\_WRITE, creates a twin for the page, and saves the twin in system space (Figure 2.9). An interval structure containing a write-notice for the page is created at the next release. A write-notice is an indication that a page has been modified. A diff of the page is then created by comparing the current version of the page with the twin. The comparison resolves differences down to the granularity of a four byte word. After the diff has been created, the twin is discarded and the page is placed back into the READ\_ONLY state.

Coherence misses occur when incoming write notices invalidate locally mapped pages. Invalidation consists of changing a page's state from READ\_ONLY or READ\_WRITE to INVALID, and removing all access rights from the page. INVALID pages differ from

Figure 2.7 Page State Transitions

UNMAPPED pages in that it is only necessary to apply a sequence of diffs to INVALID page to re-validate them. Valid pages are never made UNMAPPED.

A coherence miss indicates that at least one other processor has made changes to the page that should be reflected in the local copy before it is accessed again. In Figure 2.10, process  $P_3$  takes a coherence miss on page p, which contains data x, y, and z. Unlike conventional protocols [LH89], lazy protocols allow processes to determine the location of needed data entirely on the basis of local information.  $P_3$  is therefore able to determine that there have been two previous modifications that need to be applied locally before accessing z. Moreover,  $P_1$ 's modification of x precedes  $P_2$ 's modification of y via  $\xrightarrow{\text{hb1}}$ , so  $P_2$  must have applied  $P_1$ 's modification of x before it accessed the page to modify y. Since diffs are only discarded during garbage collection

```

if ( p READ_ONLY ) then

Allocate twin

page p ← READ_WRITE

else

if ( cold miss ) then

get copy from manager

if ( write notices ) then

Retrieve diffs

if ( write miss ) then

Allocate twin

Change protection to READ_WRITE

else

Change protection to READ_ONLY

end

```

Figure 2.8 SEGV handler for page p

(see Section 2.3.1), this information enables  $P_3$  to request both diffs from  $P_2$  rather than requesting the diffs from different sites. More generally, if processor q modified page p at interval  $\sigma_q^x$ , then q is guaranteed to have any diffs of page p created in an interval  $\sigma_s^y$ , such that  $\sigma_s^y \xrightarrow{\text{hb1}} \sigma_q^x$ . Therefore even if diffs from multiple writers need to be retrieved, it is usually only necessary to communicate with one other processor.

After the diffs have been retrieved, they are applied to the local copy of the page in an order consistent with  $\xrightarrow{hb1}$  and the process is allowed to proceed.

### Locks

"Lock" and "unlock" synchronization primitives are mapped onto the acquire and release semantic notions in a straightforward manner. Each lock has a current owner, which is the last process that acquired the lock, and a manager, which tracks the current owner. Figure 2.11 shows pseudo-code for lock acquisitions. In this figure, the notation  $wn_p$  denotes a write notice for page p.

Locks are acquired by capturing per lock *tokens*. Each process also maintains per lock fields **local** and **held** that indicate whether the token is currently owned by the process, and if so whether the lock is currently being held. If the token is local, acquiring a lock is a matter of setting a flag.

Figure 2.9 Diff Creation

**Figure 2.10** Combining diff requests (x, y, z all on page p)

```

if (local) then

held \leftarrow TRUE

return

end

Send request, with VV_a, to manager

Create new interval

Wait for grant

for each interval \sigma_q^x \ \epsilon \ \texttt{send\_set}

foreach wn_p \in \sigma_a^x

if page p READ_ONLY then

Change page p protection to INVALID

elseif page p READ_WRITE

remove from dirty_list

create write notice, if necessary

create diff for page

de-allocate twin

Change page p protection to INVALID

end

end

end

held \leftarrow local \leftarrow TRUE

```

Figure 2.11 Lock Acquisition

If the token is non-local, a request is sent to the lock's manager, which forwards the request to the last requester of the lock. Each node maintains a **next** field per lock, and in combination, the **next** fields of the nodes waiting for a given lock implement a distributed FIFO queue of waiting processors. The acquirer creates a new interval after sending the request in order to avoid interference between write notices returning from the releaser and local pages that are in a modified state. Interval creation entails adding write notices for each dirty page to a newly created interval structure. In the general case, remote lock acquisitions take three messages, but only two are needed if the manager owns the token.

An alternative to this static ownership scheme is to use an adaptive scheme that relies on guesses of the token's location, and follows successive guesses to the current owner of the token [Car93, LH89]. Since local guesses are updated to point to the requester as the request is forwarded along, every node in the chain of guesses ends up knowing which process currently owns the token, and subsequent request chains are likely to be short. However, our experience is that this type of scheme still uses more messages than the simpler manager scheme.

Figure 2.12 shows pseudo-code for the lock request handler. The request is immediately granted if the lock is not being held and the lock's token is local to the handler's processor. Granting a lock involves creating a new local interval, determining the send\_set, and sending the send\_set along with the lock grant to the requester. The request is forwarded to the last processor that had previously requested the lock if it is not local, or is already spoken for.

Figure 2.13 shows the pseudo-code for a lock release. If the lock has been requested by another processor, a new interval is created, and the **send\_set** and lock grant are sent to the requester.

```

\begin{array}{c} \textbf{if} (\ local \ ) \textbf{then} \\ \textbf{if} (\ held \ ) \textbf{then} \\ \text{save } vv_a \\ \textbf{else} \\ & Create new interval \\ & send\_set \leftarrow all intervals \sigma_q^x \ \epsilon \ vv_r \ and \ not \ \sigma_q^x \ \epsilon \ vv_a \\ & Send \ send\_set \ and \ lock \ grant \ to \ requester \\ \textbf{end} \\ \textbf{else} \\ & Forward \ request \ to \ last \ requester \\ \textbf{end} \\ \end{array}

```

### Figure 2.12 Lock Request Handler

```

Create new interval

held \leftarrow FALSE

if ( there has been a request ) then

send\_set \leftarrow all intervals \sigma_q^x \in vv_r \text{ and not } \sigma_q^x \in vv_a

Send send\_set and lock grant to requester

local \leftarrow FALSE

end

```

Figure 2.13 Lock Release

### **B**arriers

Barriers are implemented with a centralized *barrier manager* that collects arrival messages and distributes departure messages. Managers are statically assigned to barriers in round robin order.

In terms of consistency information, a worker's barrier arrival is modeled as a release by the worker followed by an acquire by the manager, while a departure is modeled as a release by the manager followed by an acquire by each of the workers. Therefore, there is a synchronization transfer from each arriving worker process to the barrier manager, and then from the manager to each of the departing workers when they are released.

Like lock releases, arrival messages include consistency information in the form of a send\_set. Unlike lock releases, arrival messages are not preceded by a request from the manager containing the manager's vector timestamp. Since the worker's knowledge of the manager's vector timestamp may be out of date, the send\_set sent on the arrival message may be larger than necessary. The manager simply discards any incoming write notices that it has already seen.

Release messages also contain **send\_sets**, but these will be no larger than necessary because the **send\_sets** on arrival messages implicitly include the workers' vector timestamps.

### **Multiple Writers**

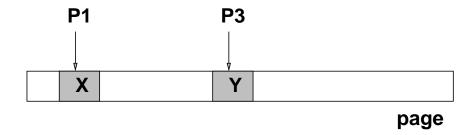

Figure 2.14 shows an example where two processors,  $P_1$  and  $P_3$ , modify logically distinct pieces of data, x, and y. Yet because the system tracks accesses at the level of virtual memory pages and these pieces of data are co-located on the same page,

Figure 2.14 False Sharing

the system must assume that the accesses are competing. In a conventional DSM that uses a single-writer, multiple-reader protocol, the page may "ping-pong" across the network because both processors will simultaneously try to gain sole ownership of the contested page.

False sharing does not cause ping-ponging under any of the protocols discussed in this chapter because they all allow multiple concurrent writers. Figure 2.15 shows how this example might be handled under a lazy protocol. Processes  $P_1$  and  $P_3$  are again modifying logically distinct pieces of data on the same page. Although  $P_1$  and  $P_3$  never communicate directly,  $P_2$  can construct a copy of the page that includes all of the changes by applying the diffs that summarize the two modifications. There is no communication between the two, and yet summarizing the modification as diffs allows  $P_2$  to update its copy of the page to reflect modifications made in both of the other processes merely by applying the diffs.

We can infer from the lack of synchronization between  $P_1$  and  $P_3$  that the sharing in this example is false sharing, because otherwise such unsynchronized accesses would constitute a data-race, and all programs that run on our system are required to be data-race-free.

Since all programs are known a priori to be data-race-free, modifications made to a page that is falsely shared are not ordered by  $\xrightarrow{hb1}$ . The modifications must

Figure 2.15 Multiple Writers: X,Y on same page

be non-overlapping because overlapping concurrent modifications would constitute a data race. Since the diffs are known to be non-overlapping, they can be applied to  $P_2$ 's copy of the page in either order without changing the final result.

### Lazy Diff Creation

We have so far implied that diffs for each dirty page are immediately created upon a lock release or barrier arrival. In fact, diffs can be created far less frequently without violating correctness.

We reduce the number of diffs created through the use of *lazy diffing*. Lazy diffing means that only a write notice is created at the time of the release; diff creation is deferred until a subsequent request for the diff or until a write notice for the same page is received from another process. Until a diff is actually created, additional modifications to the page continue to be accumulated, and the eventual diff includes all of the modifications, even those that occurred after the first release operation. The gain in performance can be considerable, because the eventual diff may include modifications that would have been split over several separate diffs in a system that did not support lazy diffing.

Reducing the number of diffs created saves considerable overhead, as diff creation in our initial environment averages about 800  $\mu$ secs a piece. A secondary benefit is that lock acquisitions are faster because grant messages are not delayed until diffs are created. Finally, reducing the number of diffs can reduce the overall amount of data sent over the network, because programs with significant temporal locality often overwrite the same locations many times, and a lazy diff will only include the last values written to each location.

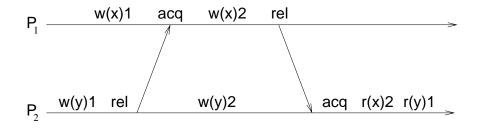

An obvious area for improvement would seem to be in combining multiple diffs of a single page into a single diff over and above the lazy diff mechanism. This would save bookkeeping, diff storage overhead, and possibly network communication. Unfortunately, diff combining is possible only in very specific circumstances.

A simple example of the problem with diff combining is illustrated by Figure 2.16.  $P_1$  combines diffs describing the results of operations w(x)1, w(y)1, and w(x)2 into a single diff. In order to satisfy its read of x,  $P_2$  must apply the combined diff. The combined diff, however, not only updates  $P_2$ 's view of x, but it overwrites y as well. Therefore,  $P_2$ 's subsequent read of y will return 1, instead of the correct value of 2.

**Figure 2.16** Bad diff combine: *x*, *y* same page

In general, diffs can only be combined in the absence of learning of new, possibly interleaving, diffs to the same page by other processors. One possible mechanism would be to allow a process,  $P_1$ , to combine a run of diffs  $diff_{1,x}^i$  through  $diff_{1,x}^j$ , where  $diff_{1,x}^i$  is the *i*th diff of page x created by processor  $P_1$ , only if there is no  $diff_{2,x}^k$  where  $diff_{2,x}^k \xrightarrow{\text{hb1}} diff_{2,x}^j$  and not  $diff_{2,x}^k \xrightarrow{\text{hb1}} diff_{2,x}^i$ . Such a mechanism can be implemented by retaining the twin even after a diff has been created, and using the twin to create subsequent diffs *until that processor receives another write notice* for the same page from another processor. Drawbacks of this technique include the overhead of retaining twins, and the increasing size of the combined diffs, and slightly complicated bookkeeping in the routines that manage diffs.

A second possibility is to discard diffs if they are completely over-written by later diffs to the same page.

Our implementation currently uses neither of the above optimizations because our results show that in our environment, per-message overhead is high enough that any possible savings from diff combining are unlikely to greatly affect overall performance.

#### Garbage Collection

In an eager system, garbage collection is unnecessary because diffs are immediately flushed to every other copy in the system, and therefore no longer needed. In a lazy system, diffs need to be retained until it is clear that the diffs will no longer be requested, i.e. the diffs have already been sent to every processor, or all copies of the page have the diff applied.

In TreadMarks, any process may request a garbage collection from the manager, which initiates the algorithm at the next global barrier, piggybacking a repo\_start message on the barrier releases. At receipt of a repo\_start message, worker processes validate every page that is not in an UNMAPPED state. Once all pages are either READ\_ONLY or UNMAPPED, a repo\_complete message is sent back to the manager. After repo\_complete messages have been collected from all workers, the manager sends out repo\_release messages and the system continues on as before. Section 3.3.2 shows that even this brute force approach costs little in terms of processor cycles.

## 2.3.2 Lazy Hybrid

The aim of the lazy hybrid protocol (LH) is to reduce the number of access misses by speculatively moving data before it is requested, rather than only in response to access misses. The central intuition is that processes synchronize in order to share data, and the flow of data is likely to mirror the flow of synchronization.

The LH differs from LI in two respects: diffs may be speculatively appended to lock grant messages, and diffs are flushed prior to barrier arrivals. This section describes only those aspects of LH that differ from LI.

# Locks

The diffs appended to grant messages are chosen by a heuristic that uses an *approximate copyset* to track access to shared pages by other processes. Copysets are initialized to the page's manager, and other processors are added when either (i) another processor requests either a diff of the page or the page itself from the local processor, or (ii) a write-notice describing a modification to that page by the remote processor is seen by the local processor. Processors are never removed from copysets.

The assumption behind the heuristic is that programs usually have significant temporal locality, and therefore any page accessed by a process in the past is likely to be accessed in the future. The heuristic therefore selects diffs of pages that the copyset indicates have been accessed by the lock destination in the past. The search for diffs is limited to diffs corresponding to write notices in the send\_set. Any diffs that do not fit into the lock grant message are sent in additional unacknowledged messages. The additional messages can be unacknowledged because they do not contain consistency information, and therefore do not violate correctness if lost.

# Barriers

Prior to barrier arrivals, processes under the LH protocol *flush* likely diffs to all other processes in the system. Figure 2.17 shows pseudo-code for the flush procedure.

The flush procedure creates a send\_set analogous to the lock send\_set for each of the other processes in the system. For each of the processes, the flush sends diffs corresponding to all write notices in the send\_set that were created by the flushing process. The flush operation may take multiple messages, and the messages are not acknowledged because their loss affects only performance, not correctness.

# Lazy Diffing

The hybrid protocol also uses the lazy diffing mechanism, but to less benefit. Because of lazy diffing, diffs describing recent modifications are unlikely to have been created yet. In order to have the hybrid make a significant impact on performance, LH overrides the lazy diffing mechanism and creates any diffs selected by the heuristics. This can result in many more diffs being created under LH than LI, as well as larger lock acquisition latencies.

## 2.3.3 Eager Invalidate

We base our eager RC algorithms on Munin's multiple-writer protocol [CBZ91]. RC requires all prior ordinary accesses to be globally performed before a subsequent release is performed at any other process. The EI protocol calls a *flush* operation prior to any release. The **flush** operation sends invalidates to all other processes in the system that cache the affected pages. Since the local process may not have complete information on page replication, multiple rounds may be necessary to ensure that the

```

foreach p \in (system processes)

diffs \leftarrow \emptyset

foreach wn \in (send\_set to p)

if (creator(wn) = ME) then

diffs \leftarrow diffs + diff(wn)

end

Send diffs unreliably to p

end

```

Figure 2.17 Hybrid Barrier Flush

invalidates are performed on all copies of the page. Once the invalidate messages have been received and acknowledged, the release operation is allowed to proceed.

# Locks

Under EI, synchronization messages carry no consistency information, and there is no eager equivalent of the send\_set. Since the consistency action takes place at the release during the flush operation, an acquire consists solely of locating the process that executed the last prior release and transferring the synchronization variable. Lock ownership is determined as under the lazy protocols, taking either two or three messages to return the lock grant.

#### Barriers

Processes arriving at a barrier call the flush operation prior to sending arrival messages to the manager. Barrier messages therefore contain no consistency information.

#### Access Misses

The EI protocol handles page ownership analogously to lock ownership. Each page has a statically assigned manager, but ownership of the page dynamically shifts according to access patterns. Page ownership differs from lock ownership in that the owner of a page does not have an exclusive copy of the page. Instead, the "owner" of a page is defined as the most recent process to request a copy from the manager.

Figure 2.18 shows a state transition diagram for shared pages. Pages are in one of three states: READ\_ONLY, READ\_WRITE or INVALID. Initially, the page is READ\_ONLY at the manager and INVALID everywhere else. The owner is initially set to the manager. Processes taking an access miss request a copy of the page from the page's manager. If the manager's copy is not INVALID, the copy is returned directly to the missing process. Otherwise, the manager forwards the request to the current owner, which responds with a copy of the page. In either case, the process that incurred the access miss is designated the new owner, and the state of the new owner's copy is set to either READ\_ONLY or READ\_WRITE, depending on the type of the access.

When a write is attempted to a READ\_ONLY page, a copy (twin) of the page is created and the page's state is set to READ\_WRITE. A flush operation discards all twins, sets the twinned pages' state back to READ\_WRITE, and sends invalidation messages to all other processes that have copies of the affected pages. If an invalidate for

Figure 2.18 RC Page State Transitions

a READ\_WRITE page is received, a diff of the page is created and returned to the invalidator on the invalidate reply, and the local copy of the page becomes INVALID.

# The flush Operation

The flush operation ensures that any prior local modifications are performed globally. The modifications are performed by sending invalidations to all other processes that cache the affected pages. Since local information about page caching may be out of date, each process appends their copyset for the invalidated pages to their acknowledgment. The returned information is used to direct additional rounds, if necessary.

If an invalidate is received for a page that is locally in state READ\_ONLY, the page state is set to INVALID and read permission is removed. If the page was in state READ\_WRITE, a diff is created to describe local modifications, and then the page state and permissions are changed as for READ\_ONLY. The diff is returned on the acknowledgment message. If there is not sufficient space in the acknowledgment message to copy the diff, an indication that the diff is available is returned instead. The invalidating process then explicitly requests the diff(s) with another pair of messages.

The protocol becomes greatly complicated when multiple processors attempt to concurrently invalidate the same pages. One of these processes may be unaware of the other until after flush completes, and either or both of the processes may receive diffs from other processes. In this case, the protocol resorts to flushing all diffs to all processes in order to insure that at least one process retains a valid copy of the page, and that diffs are applied to every copy that remains. We observed this global system update occuring in only one of our programs.

Strictly speaking, this implementation *performs* ordinary accesses earlier than necessary, thereby reducing the opportunity for overlap of communication and computation. Definition 2.2 only requires ordinary accesses to be performed when a subsequent release operation is performed. By definition, however, a release is not performed until the same lock is acquired by another process. Therefore, the **flush** operation is not required to complete until the lock is requested by another process. However, allowing the flush to operate concurrently with the computation would either increase lock acquisition latency when **flush** requires multiple rounds, or incur additional signal handling overhead. In either case, the protocol is greatly complicated.

# 2.4 Correctness

This section presents a proof that LI guarantees sequentially consistent executions for all data-race-free programs, where a sequentially consistent execution is an execution, or a specific run, of a program that could have been produced by an SC system. The proof for LH is identical.

This proof is based on a result by Adve [Adv93] that any system meeting a specific set of sufficient conditions guarantees to produce only sequentially consistency executions. The rest of this section re-caps some necessary definitions and then shows by inspection that LI meets the required sufficient conditions, and therefore guarantees SC executions.

DRF1 distinguishes synchronization and non-synchronization operations without imposing any restrictions on *how* they are distinguished. Synchronization operations are either *releases* or *acquires* of synchronization variables. Everything else is a data operation. Intuitively, a program is correct if *enough* operations are distinguished as releases or acquires. In this context, "enough" means that the resulting program has no data races, or is data-race-free (Definition 2.5). Definition 2.6 and Condition 2.4.1 are from Adve's thesis [Adv93].

**Definition 2.6** A system obeys the *data-race-free-1* memory model if and only if the result of every execution of a data-race-free program on the hardware can be obtained by an execution of the program on sequentially consistent hardware.

Adve showed that any DRF1 system guarantees sequentially consistent executions for all data-race-free programs. Therefore, all that remains is to show that a system using the LI protocol is indeed a DRF1 system.

Condition 2.4.1 specifies sufficient conditions for a system to obey the DRF1 memory model.

**Condition 2.4.1** Hardware obeys the data-race-free-1 memory model if for every execution,  $E_{drf}$ , of a program, Prog, on the hardware, there is an  $\xrightarrow{\text{xo}}$  (and a corresponding  $\xrightarrow{\text{hb0}}^{\text{hb0}}$ ) that satisfy the following conditions: (i) Data - If X and Y are conflicting operations, at least one of X or Y is a data operation, and  $X \xrightarrow{\text{hb1}} Y$ , then  $X(i) \xrightarrow{\text{xo}} Y(i)$  for all i.

(ii) Synchronization - If X and Y are conflicting synchronization operations, and  $X \xrightarrow{\text{hb0}} Y$ , then  $X(i) \xrightarrow{\text{xo}} Y(i)$  for all i.

(iii) Control - If Prog is data-race-free, then there exists a sequentially consistent execution,  $E_{sc}$ , with a well-formed  $\xrightarrow{\text{xo}}$  and a corresponding  $\xrightarrow{\text{hb0}}$  such that (i) an operation is an  $E_{drf}$  iff it is in  $E_{sc}$ , (ii) for two conflicting operations X and Y, such that at least one of them is a data operation, if  $X \xrightarrow{\text{hb1}} Y$  in  $E_{sc}$ , then  $X \xrightarrow{\text{hb1}} Y$  in  $E_{drf}$ , and (iii) for two conflicting synchronization operations X and Y, if  $X \xrightarrow{\text{hb0}} Y$  in  $E_{sc}$ , then  $X \xrightarrow{\text{hb0}} Y$  in  $E_{sc}$ , then  $X \xrightarrow{\text{hb0}} Y$  in  $E_{sc}$ , then  $X \xrightarrow{\text{hb0}} Y$  in  $E_{drf}$ .

The notation X(i) refers to the  $i^{th}$  sub-operation of X. A sub-operation is the performance of the operation at a specific remote site. The notation  $\xrightarrow{x_0}$  refers to execution order.

The "data requirement" specifies that conflicting updates are done atomically with respect to one another. This requirement is fulfilled by LI because overlapping

<sup>\*</sup>The ordering  $\xrightarrow{hb0}$  differs from  $\xrightarrow{hb1}$  in that  $\xrightarrow{hb0}$  is specific to a single execution, while  $\xrightarrow{hb1}$  applies to all executions of a given program. To avoid confusion,  $\xrightarrow{hb1}$  is used in the rest of the text. See [Adv93] for the original definitions.

modifications are totally ordered by  $\xrightarrow{hb1}$ , and diffs are always requested and applied in an order consistent with  $\xrightarrow{hb1}$ .

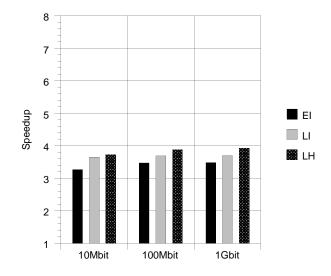

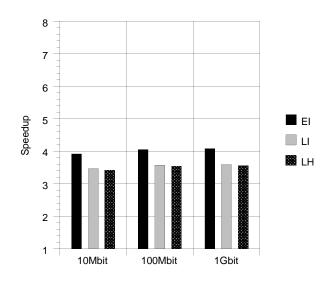

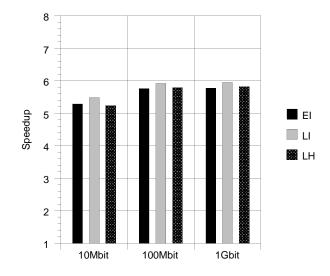

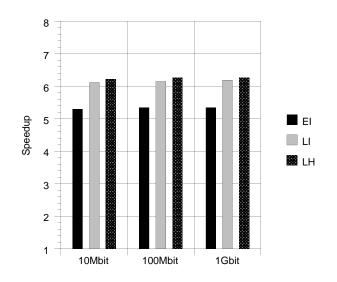

The "synchronization requirement" specifies that synchronization operations are sequentially consistent with one another. This requirement is met by observing that all LI synchronization operations are SC with respect to one another, because each operation completes atomically before a synchronization variable can be accessed by another process<sup>†</sup>.